TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC90A49P,TC90A49F

3LINE DIGITAL Y / C SEPARATOR IC (MULTICOLOR TYPE)

The TC90A49P / F is a 3-line digital Y / C (luminance / chrominance) separation IC for PAL, NTSC, M-PAL and N-PAL format.

## FEATURES

- TV format : NTSC (3.58), PAL, M-PAL, and N-PAL

- Dynamic comb filter

- Vertical edge enhancement circuit

- PLL 8 × multiplier circuit

- Internal 8-bit 4 fsc AD converter

- Internal 8-bit precision 8 fsc DA converter (2 ch)

- Sync tip clamp circuit

- Internal 4H-line memory

- I<sup>2</sup>C bus interface

- Package : DIP 20-pin and SOP 24-pin

- 5 V single power supply

000707EBA1

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or

to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss or numan life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.. • The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. shall be made at the customer's own risk.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or a strength or otherwise under a strength or otherwise others

The information contained herein is subject to change without notice.

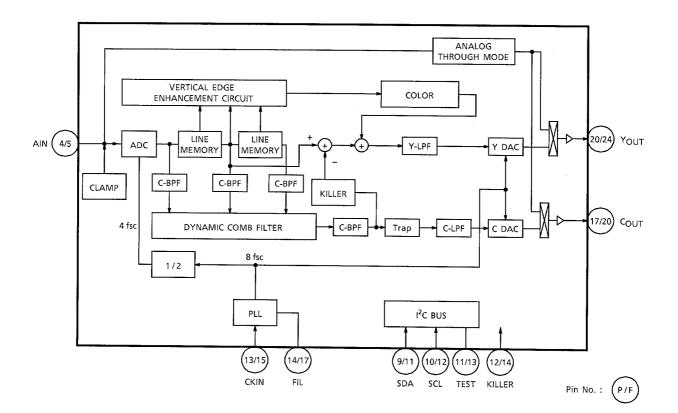

## **BLOCK DIAGRAM**

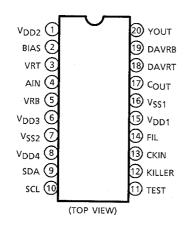

## **PIN ASSIGNMENT**

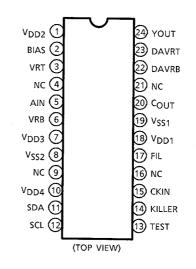

TC90A49F

The NC which was writting in PIN ASSIGNMENT must use the open condition.

# <u>TOSHIBA</u>

# **PIN DESCRIPTION**

no. before / indicates DIP package pin no. no. after / indicates SOP package pin no.

| PIN<br>No. | PIN NAME         | FUNCTION                                                                             | I / O | INTERFACE |

|------------|------------------|--------------------------------------------------------------------------------------|-------|-----------|

| 1          | V <sub>DD2</sub> | ADC and DAC analog power supply.                                                     | -     | -         |

| 2          | BIAS             | ADC bias voltage.<br>Stabilize by attaching a 0.01µF capacitor.                      | -     |           |

| 3          | VRT              | ADC input range D upper limit voltage.<br>Stabilize by attaching a 0.01µF capacitor. | -     |           |

| 4 / 5      | AIN              | ADC input. Inputs 1.0 V <sub>p-p</sub> video signal.<br>Sync tip clamp is performed. | I     |           |

| 5/6        | VRB              | ADC input range D lower limit voltage.<br>Stabilize by attaching a 0.01µF capacitor. | -     |           |

| 6 / 7      | V <sub>DD3</sub> | ADC and DAC logic power supply.                                                      | -     | -         |

| 7 / 8      | V <sub>SS2</sub> | Logic and internal DRAM GND (digital).                                               | -     | -         |

| 8 / 10     | V <sub>DD4</sub> | Internal DRAM power supply.                                                          | -     | -         |

| 9 / 11     | SDA              | I <sup>2</sup> C BUS SDA                                                             | 1/0   |           |

| 10 / 12    | SCL              | I <sup>2</sup> C BUS SCL                                                             | I     |           |

| PIN<br>No. | PIN NAME         | FUNCTION                                                                                                                                                                                                                                            | I / O | INTERFACE |

|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|

| 11 / 13    | TEST             | Shipment test mode switch or $I^2C$ bus setting reset pin.<br>When High, test mode, setting all $I^2C$ bus settings to 0.<br>Hold High for at least 100µs. Send $I^2C$ bus settings<br>when this pin is Low.                                        | I     |           |

| 12 / 14    | KILLER           | Y signal comb function ON / OFF switch.<br>When High, comb OFF. When Low, comb ON. When<br>[data 3 : bit 0] is 1, used as vertical edge enhancement<br>circuit ON / OFF switch.                                                                     | I     |           |

| 13 / 15    | CKIN             | Clock input pin. Pin 13 put a sine wave which is locked to the frequency of the burst signal in the input video signal. Amplitude is 300 mV $_{p-p}$ to 2 $V_{p-p}$ . Input as high an amplitude as possible without affecting peripheral circuits. | I     |           |

| 14 / 17    | FIL              | Connect the APC filter in the 8 fsc PLL circuit.                                                                                                                                                                                                    | -     |           |

| 15 / 18    | V <sub>DD1</sub> | PLL power supply.                                                                                                                                                                                                                                   | Ι     | -         |

| 16 / 19    | V <sub>SS1</sub> | ADC, DAC, and PLL GND (analog).                                                                                                                                                                                                                     | _     | -         |

| 17 / 20    | C <sub>OUT</sub> | Outputs chrominance signal. External simple LPF for clock elimination recommended.                                                                                                                                                                  | 0     |           |

| PIN<br>No. | PIN NAME | FUNCTION                                                                              | 1/0 | INTERFACE           |

|------------|----------|---------------------------------------------------------------------------------------|-----|---------------------|

| 18 / 22    | DAVRT    | DAC output range D upper limit voltage.<br>Stabilize by attaching a 0.01µF capacitor. | -   |                     |

| 19 / 23    | DAVRB    | DAC output range D lower limit voltage.<br>Stabilize by attaching a 0.01µF capacitor. | -   |                     |

| 20 / 24    | Yout     | Outputs luminance signal. External simple LPF for clock elimination recommended.      | 0   | 20/24<br>OP<br>amp. |

## FUNCTION DESCRIPTION (Pin no. in this section refers to DIP package pin no.)

### 1. AD converter (ADC)

High-speed 8-bit AD converter. The input dynamic range is  $1.3 V_{p^p}$  (max) = 256 steps. They recommends input of video signals of  $1.0 V_{p^p}$  (from sync tip level to 100% white level).

### 2. Clamp circuit

Performs sync tip clamp of the input video signal. The clamp level is determined internally to use the ADC dynamic range efficiently.

### 3. Line memory

Incorporates DRAM-resident, four 1-H delay circuits. Combination of delay circuits and delay times are determined according to the signal format selected by the  $I^2C$  bus.

| TV Format            | NTSC | PAL  | N-PAL | M-PAL |

|----------------------|------|------|-------|-------|

| Delay Amount (clock) | 910  | 1135 | 917   | 909   |

### 4. Band pass filter (BPF)

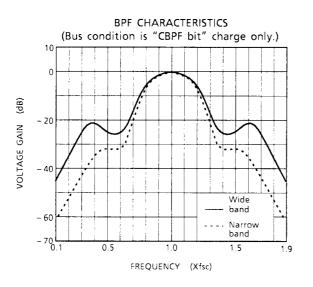

Extracts the chrominance signal from the line-memory-delayed composite video signal. The same filter is used by NTSC, PAL, M-PAL, and N-PAL formats. The center frequency is fsc. The characteristics differ depending on the TV format. BPFs are provided for both input and output sides of the dynamic comb filter. The input side can be set to a wide band. The output side can be set to either a wide or a narrow band using the  $I^2C$  bus control.

### 5. Dynamic comb filter (DCF)

Using Toshiba's original decision logic, detects a correlation of the three consecutive vertical lines for NTSC, every other three lines for PAL, and extracts the chrominance signal accordingly.

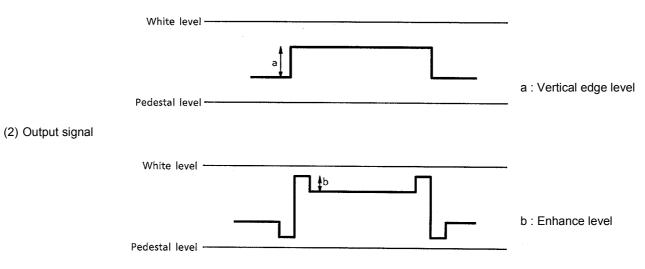

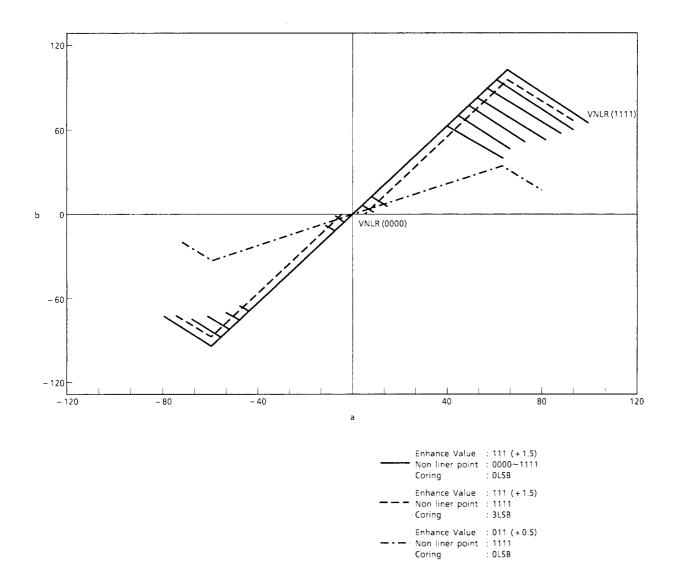

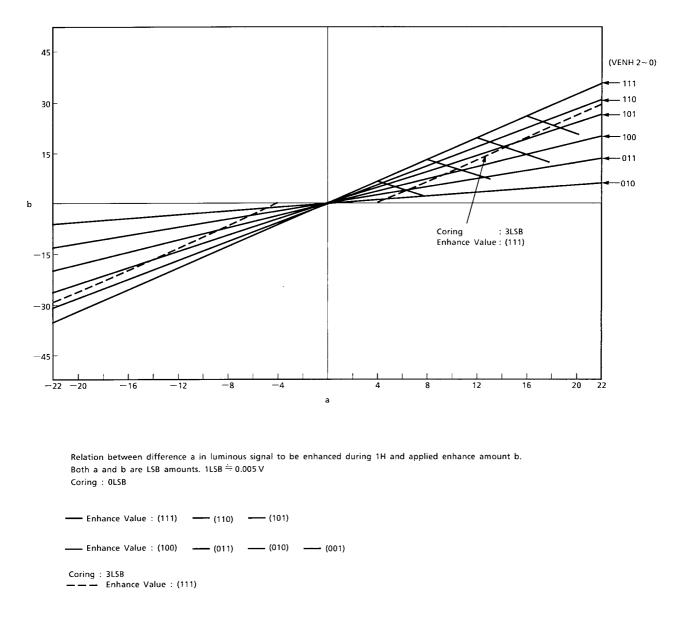

#### 6. Vertical edge enhancement circuit

Generates edge components in proportion to the luminance differential signal of the three consecutive vertical lines and adds the components to the luminance signal output. There are eight enhancement levels selected by the  $I^2C$  bus. The coring circuit eliminates differential signals caused by noise; thus, increase in noise due to edge enhancement is reduced. Signals lower than the pedestal level due to the addition of the edge enhancement signal may be generated; however, such signals are eliminated by the pedestal clip circuit at a later stage. Therefore, there is no adverse effect on the sync processor circuit. The coring circuit regards small edge components as noise and does not perform enhancement.

(1) Input signal with edge component

## Vertical edge enhancement characteristic

## Vertical edge enhancement characteristic (Zoom)

#### 7. PLL 8 × multiplier circuit

Multiplies by eight the input subcarrier signal which is locked to the frequency of burst signal to generate 8 fsc and 4 fsc system clocks.

### 8. DA converter (DAC)

The Y / C signal separated using the 4 fsc clock as the basic clock is over-sampled by the 8 fsc clock, then DA-converted.

### 9. Color killer circuit

When the input video signal is a monochrome image, this circuit enables effective use of the luminance signal information regardless of whether there is a burst signal. It does this by preventing the chroma signal output from the comb filter from being subtracted from the luminance signal.

While the VBI signal is active it is better not to use the comb function. Setting the KILLER pin to High at this time enables the use of character multiplex and other signals from the Y output unchanged.

### 10. RESET / TEST pin

Switches between normal comb operation and test operation. Also used for  $I^2C$  bus reset input. Change in voltage from Low to High triggers a reset. Normal use is Low.

# 11. I<sup>2</sup>C bus interface

Some functions and setting values can be selected using the  $I^2C$  bus. The data transfer format conforms to the Philips  $I^2C$  bus format.

### Data transfer format

| S | Slave address (8 bit)                    | А | DATA1              | А    | DATA2  | А     | DATA3   | А | Ρ |

|---|------------------------------------------|---|--------------------|------|--------|-------|---------|---|---|

|   | S : start condition<br>Slave address : B |   | A : acknowle<br>X) | edge | P : er | nd co | ndition |   |   |

# 12. I<sup>2</sup>C bus control contents : When a reset signal is input, all the following bits are zero-cleared.

|       | MSB<br>bit7       | bit6              | bit5              | bit4              | bit3              | bit2              | bit1             | LSB<br>bit0      |

|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| DATA1 | MODE <sub>2</sub> | MODE <sub>1</sub> | MODE <sub>0</sub> | VENH <sub>2</sub> | VENH <sub>1</sub> | VENH <sub>0</sub> | PDSOFF           | CB               |

| DATA2 | VNLR <sub>3</sub> | VNLR <sub>2</sub> | VNLR <sub>1</sub> | VNLR <sub>0</sub> | GSEL1             | GSEL0             | COR <sub>1</sub> | COR <sub>0</sub> |

| DATA3 | TRAP              | CHTRAP            | Fixed to 0        | CBPF              | Fixed to 0        | Fixed to 0        | Fixed to 0       | ENHOFF           |

Mode 2 to Mode 0 : Select video signal format.

000 : Analog Through Mode 001 : M-PAL 010 : N-PAL 011 : PAL 100 : NTSC

When Analog Through mode is selected, input video signals are output to Yout and Cout unchanged. In Analog Through mode, the delay time for output signals differs from those used for other modes. Therefore, when changing modes to Analog Through mode, to decide the input signal format, provide some delay time until an image is displayed.

There is a case where a 1 LSB error voltage at frequency fsc is multiplexed with the output signal. When deciding the input signal format, to avoid an erroneous decision due to fsc leakage, be careful when setting the decision sensitivity (killer sensitivity).

When the input signal is SECAM or 4.43 NTSC, select Analog Through mode. A separate BELL filter or a BPF is required.

VENH<sub>2</sub> to VENH<sub>0</sub> : Set vertical enhancer gain. 000 : (+0.0) to 111 : (+1.5) PDSOFF : Switches pedestal clip ON / OFF after vertical edge enhancement circuit. 0:ON1:OFFCB: Sets Color Killer mode to ON / OFF 0: Y signal comb function ON 1: Y signal comb function OFF (Same composite signal is output from Y and C pins.) VNIR<sub>3</sub> to VNIR<sub>0</sub> : Set vertical enhancer non-linear point. 0000: 4 LSB (internal set of IC to 4 LSB) to 1111: 64 LSB (internal set of IC to 64 LSB) GSEL1 : Sets Y output horizontal peaking gain. 0: 1.5 dB 1:3.0 dB  $\operatorname{GSEL}_0$  : Switches Y output horizontal peaking ON / OFF. 0:ON1:OFFCOR1 and COR0 : Set vertical enhancer coring level. 00:0 LSB to 11:3 LSB TRAP : Sets C output 1 / 2 fsc trap ON / OFF. 0:ON1:OFFCHTRAP : Sets C output trap gain. 0:-24 dB 1:-16 dB CBPF: Switches C output BPF ON / OFF (BPF characteristic after dynamic comb filter output). 0: Narrow band = BPF  $\rightarrow$  ON 1 : Wide band = BPF  $\rightarrow$  OFF ENHOFF: Sets KILLER pin function. 0: Comb ON / OFF 1: Comb ON / OFF and vertical edge enhancement ON / OFF

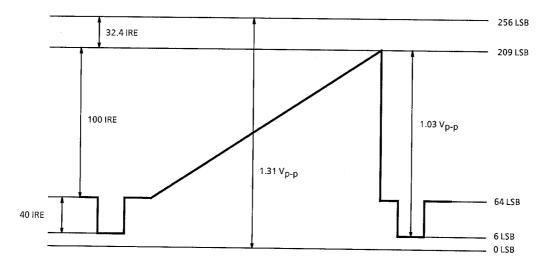

#### Signal level inside the IC

The sync tip of the input video signal is clamped to an internal level equivalent to 6 LSB. When a signal amplitude of 1.0 V is equivalent to 140 IRE, 100% white status becomes an internal level of 209 LSB. At this time, the input dynamic range of 256 LSB is equivalent to  $1.3 V_{p-p}$ .

## MAXIMUM RATINGS (Ta = 25°C)

| CHARACTE                     | RISTIC |       | SYMBOL             | RATING                | UNIT |

|------------------------------|--------|-------|--------------------|-----------------------|------|

| Power Supply Voltage         |        |       | V <sub>DD</sub>    | V <sub>SS</sub> + 6.0 | V    |

| Max                          |        |       | V <sub>inmax</sub> | V <sub>DD</sub> + 0.3 | V    |

| Pin Voltage                  |        | Min   | V <sub>inmin</sub> | V <sub>SS</sub> – 0.3 | v    |

| Power Dissipation            | 49P (N | lote) | PD                 | 550                   | mW   |

| Power Dissipation 49F (Note) |        |       | PD                 | 458                   | mW   |

| Storage Temperature          |        |       | T <sub>stg</sub>   | -55~125               | °C   |

(Note) : Ta = 70°C

## **RECOMMENDED OPERATING CONDITIONS**

| CHARACTERISTIC        | SYMBOL           | MIN  | TYP. | MAX             | UNIT | NOTE |

|-----------------------|------------------|------|------|-----------------|------|------|

| Power Supply Voltage  | V <sub>DD</sub>  | 4.75 | 5.0  | 5.25            | V    |      |

| Digital Input Voltage | V <sub>DIN</sub> | 0    | -    | V <sub>DD</sub> | V    |      |

| Operating Temperature | T <sub>opr</sub> | -10  | -    | 70              | °C   |      |

## ELECTRICAL CHARACTERISTICS (Pin no. corresponds to DIP package pin no.) DC CHARACTERISTICS

(Ta = 25°C,  $V_{DD}$  = 5.0 V, CKIN = 3.58 MHz, 1.0  $V_{p-p}$  input,  $A_{in}$  = no input, in all modes)

| CHARACTERISTIC       | SYMBOL          | MIN  | TYP. | MAX  | UNIT | NOTE                                      |

|----------------------|-----------------|------|------|------|------|-------------------------------------------|

| Power Supply Current | I <sub>DD</sub> | 40   | 75   | 85   | mA   | Supply current, in all modes              |

|                      | V <sub>2</sub>  | 0.5  | 1.3  | 2.1  | V    | Pin 2 : ADC bias                          |

|                      | V <sub>3</sub>  | 2.85 | 3.15 | 3.48 | V    | Pin 3 : AD range D upper limit            |

| Pin Voltage          | V <sub>4</sub>  | 1.65 | 1.85 | 2.02 | V    | Pin 4 : A <sub>in</sub> input pin voltage |

| Fill Voltage         | $V_5$           | 1.65 | 1.85 | 2.02 | V    | Pin 5 : AD range D lower limit            |

|                      | V <sub>18</sub> | 2.85 | 3.15 | 3.48 | V    | Pin 18 : DA range D upper limit           |

|                      | V <sub>19</sub> | 1.65 | 1.85 | 2.02 | V    | Pin 19 : DA range D lower limit           |

## **DC CHARACTERISTICS**

(Ta = 25°C,  $V_{DD}$  = 5.0 V, CKIN = each fsc,  $A_{in}$  = no input, unless otherwise specified, in all modes)

| CHARACTERISTIC | SYMBOL           | MIN  | TYP. | MAX  | UNIT | NOTE                      |

|----------------|------------------|------|------|------|------|---------------------------|

| Output Voltage | Yout             | 1.65 | 1.85 | 2.02 | V    | Pin 20 : Y <sub>OUT</sub> |

| Output voltage | C <sub>OUT</sub> | 1.65 | 1.85 | 2.02 | V    | Pin 17 : C <sub>OUT</sub> |

# <u>TOSHIBA</u>

## **DC CHARACTERISTICS**

(Ta = 25°C,  $V_{DD}$  = 5.0 V, CKIN = each fsc,  $A_{in}$  = no input, unless otherwise specified, in all modes)

| CHARACTERISTIC           | SYMBOL           | MIN  | TYP. | MAX  | UNIT | NOTE                      |

|--------------------------|------------------|------|------|------|------|---------------------------|

| Output Voltage           | Y <sub>OUT</sub> | 1.65 | 1.85 | 2.02 | V    | Pin 20 : Y <sub>OUT</sub> |

| ouput voltage            | C <sub>OUT</sub> | 2.25 | 2.5  | 2.67 | V    | Pin 17 : C <sub>OUT</sub> |

| FIL Pin (pin 14) Voltage | V <sub>14</sub>  | -    | 2.2  | -    | V    | NTSC mode 3.579545 MHz    |

| FIL Pin (pin 14) Voltage | V <sub>14</sub>  | -    | 2.4  | -    | V    | PAL mode 4.433619 MHz     |

| FIL Pin (pin 14) Voltage | V <sub>14</sub>  | -    | 2.2  | -    | V    | M-PAL mode 3.575611 MHz   |

| FIL Pin (pin 14) Voltage | V <sub>14</sub>  | _    | 2.2  | _    | V    | N-PAL mode 3.582056 MHz   |

### PLL CHARACTERISTICS

(Ta = 25°C,  $V_{DD}$  = 5.0 V, CKIN = 1.0 Vp-p input,  $A_{in}$  = no input, unless otherwise specified, in all modes)

| CHARACTERISTIC                     | SYMBOL | MIN | TYP. | MAX  | UNIT             | NOTE                                |

|------------------------------------|--------|-----|------|------|------------------|-------------------------------------|

| Pull-in Frequency Range<br>(NTSC)  | ∆fckN  | -   | -    | ±100 | kHz              | In relation to fsc center frequency |

| Pull-in Frequency Range<br>(PAL)   | ∆fckP  | -   | -    | ±100 | kHz              | In relation to fsc center frequency |

| Pull-in Frequency Range<br>(NPAL)  | ∆fckN  | -   | -    | ±100 | kHz              | In relation to fsc center frequency |

| Pull-in Frequency Range<br>(MPAL)  | ∆fckM  | -   | -    | ±100 | kHz              | In relation to fsc center frequency |

| Input Amplitude<br>(fsc sine wave) | Vck    | 0.3 | 1.0  | 2.0  | V <sub>p-p</sub> |                                     |

# DIGITAL CHARACTERISTICS (Ta = 25°C, V<sub>DD</sub> = 5.0 V)

| CHARACTERISTIC        | SYMBOL          | MIN | TYP. | MAX | UNIT | NOTE                  |

|-----------------------|-----------------|-----|------|-----|------|-----------------------|

| Input Voltage         | V <sub>IH</sub> | 4   | -    | -   | V    | Pin 9, Pin 10, Pin 12 |

|                       | V <sub>IL</sub> | -   | -    | 1   | V    | Pin 9, Pin 10, Pin 12 |

| Current at ACK Output | Ack             | 4   | -    | -   | mA   | Pin 9 VOLmax : 0.4 V  |

# AC CHARACTERISTICS (Ta = $25^{\circ}$ C, V<sub>DD</sub> = 5.0 V, CKIN = 1.0 V<sub>p-p</sub> input) (1)Y Input (A<sub>in</sub> = input, unless otherwise specified, in all modes except Analog Through Mode)

|                                       | CHARACTERISTIC                                  | SYMBOL           | MIN  | TYP. | MAX  | UNIT | NOTE                                                    |

|---------------------------------------|-------------------------------------------------|------------------|------|------|------|------|---------------------------------------------------------|

|                                       | AD Input Top Level                              | V <sub>ADt</sub> | 2.85 | 3.15 | 3.48 | V    |                                                         |

| Input                                 | AD Input Bottom Level                           | V <sub>ADb</sub> | 1.65 | 1.85 | 2.02 | V    |                                                         |

| D Range                               | AD Input Difference<br>Between Top and Bottom   | V <sub>AD</sub>  | -20  | -    | +20  | mV   |                                                         |

|                                       | YDA Output Top Level                            | V <sub>DAt</sub> | 2.85 | 3.15 | 3.48 | V    |                                                         |

| Output                                | YDA Output Bottom Level                         | V <sub>DAb</sub> | 1.65 | 1.85 | 2.02 | V    |                                                         |

| D Range                               | YDA Output Difference<br>Between Top and Bottom | V <sub>DA</sub>  | -20  | -    | +20  | mV   |                                                         |

| Y <sub>OUT</sub> Low                  | Frequency Gain                                  | GY               | -0.5 | 0.0  | 0.5  | dB   | Input / output gain<br>measured in ADDA<br>Through mode |

| Y <sub>OUT</sub> Frequ<br>(Peaking O  | uency Characteristic<br>FF)                     | FW               | -    | 4.7  | -    | MHz  | -3 dB frequency                                         |

| Y <sub>OUT</sub> Frequ<br>(Peaking 1. | uency Characteristic<br>5 dB)                   | FW1              | -    | 6.2  | -    | MHz  | -3 dB frequency                                         |

| Y <sub>OUT</sub> Frequ<br>(Peaking 3. | uency Characteristic<br>0 dB)                   | FW2              | -    | 6.7  | -    | MHz  | -3 dB frequency                                         |

| Y <sub>OUT</sub> Com                  | b Characteristic                                | Y <sub>com</sub> | 40   | 45   | -    | dB   | Difference between comb top and bottom                  |

| Y <sub>OUT</sub> Differ               | rential Accidental                              | L                | -1   | 0    | +1   | LSB  | (Reference value)                                       |

| Y <sub>OUT</sub> Integral Accidental  |                                                 | В                | -3   | 0    | +3   | LSB  | (Reference value)                                       |

| Output Imp                            | edance                                          | Zy               | 300  | 600  | 900  | Ω    |                                                         |

# (2)C Output ( $A_{in}$ = input, unless otherwise specified, in all modes except Analog Through Mode)

| CHARACTERISTIC                               | SYMBOL            | MIN  | TYP. | MAX   | UNIT | NOTE                                   |

|----------------------------------------------|-------------------|------|------|-------|------|----------------------------------------|

| Output Dynamic Range                         | VC <sub>OUT</sub> | -    | 1.0  | 1.0   | V    | D Range of C                           |

| C <sub>OUT</sub> Gain Input                  | GC                | -0.5 | 0.0  | + 0.5 | dB   | Output gain at comb operation          |

| C <sub>OUT</sub> Gain Comb<br>Characteristic | C <sub>com</sub>  | 35   | 40   | -     | dB   | Difference between comb top and bottom |

| Differential Gain                            | DG                | 0    | 2    | 5     | %    |                                        |

| Differential Phase                           | DP                | 0    | 2    | 5     | 0    |                                        |

| Output Impedance                             | Zc                | 300  | 600  | 900   | Ω    |                                        |

## (3)CHARACTERISTICS BY BUS SETTING (A<sub>in</sub> = input, unless otherwise specified, in all modes except Analog Through Mode)

| CHARACTERISTIC                        | SYMBOL          | MIN | TYP. | MAX | UNIT | NOTE                        |

|---------------------------------------|-----------------|-----|------|-----|------|-----------------------------|

| C-BPF Characteristic<br>(Wide Band)   | BW <sub>1</sub> | -   | -2.5 | -   | dB   | Attenuation at fsc -0.5 MHz |

| C-BPF Characteristic<br>(Narrow Band) | BW <sub>0</sub> | _   | -3.0 | -   | dB   | Attenuation at fsc -0.5 MHz |

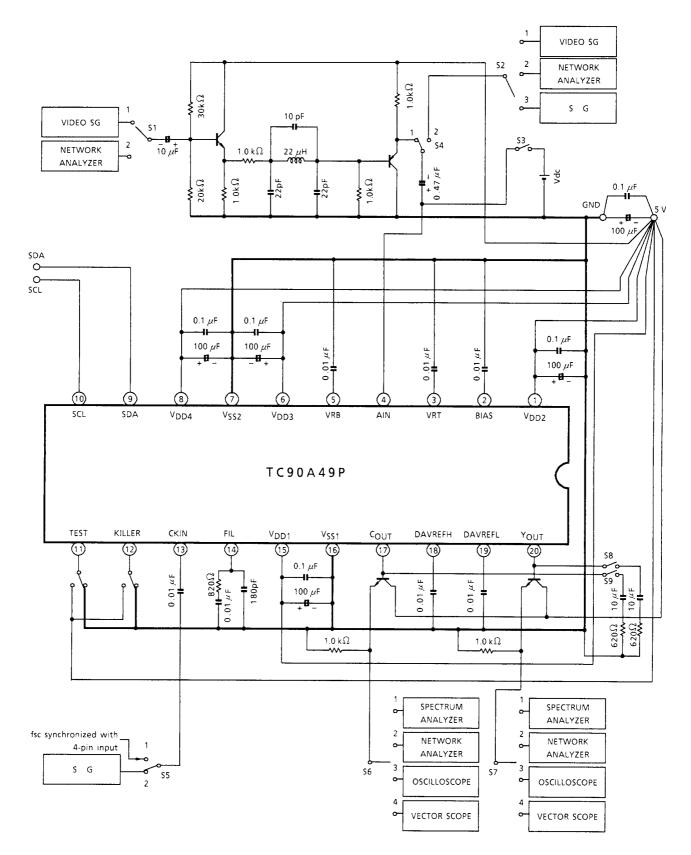

# TEST CIRCUIT (TC90A49P)

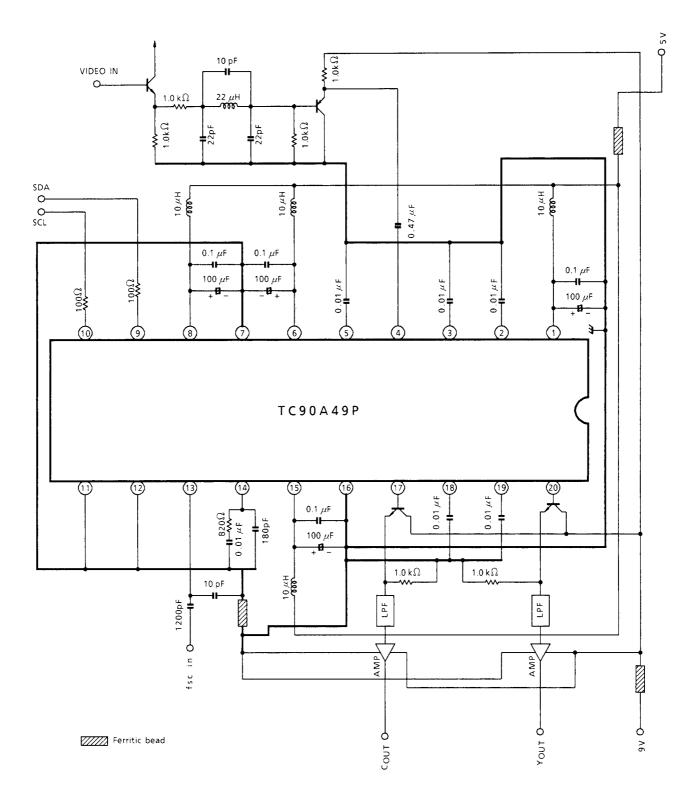

# **APPLICATION CIRCUIT (TC90A49P)**

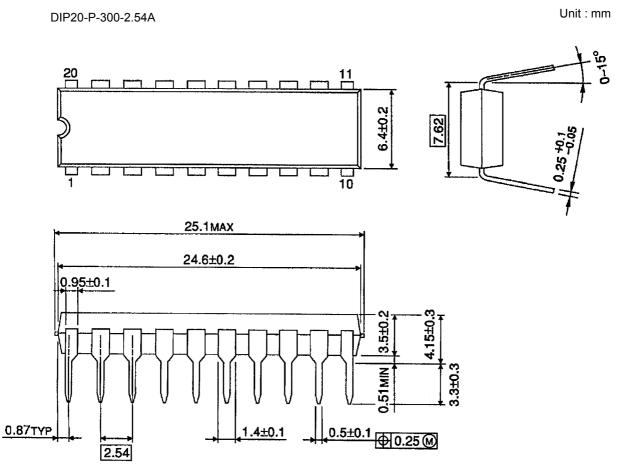

# PACKAGE DIMENSIONS

Weight : 1.11g (Typ.)

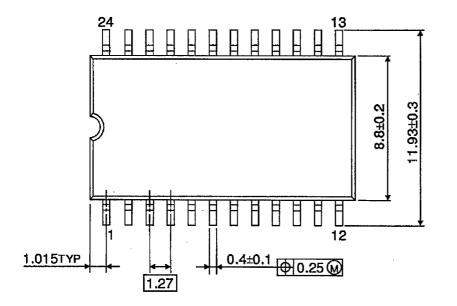

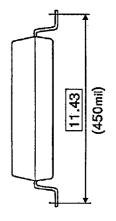

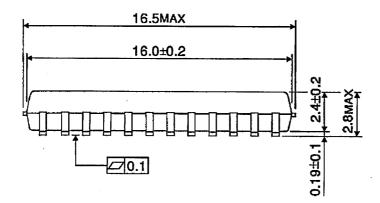

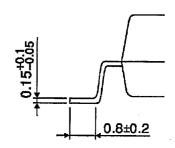

# PACKAGE DIMENSIONS

SOP24-P-450-1.27B

Unit : mm

Weight: 0.44g (Typ.)